はんだ材料

J-STD-003 (PCBはんだ付性)

J-STD-003:はんだ付け性試験(PCB)

プリント基板のはんだ付け性試験(国際規格)

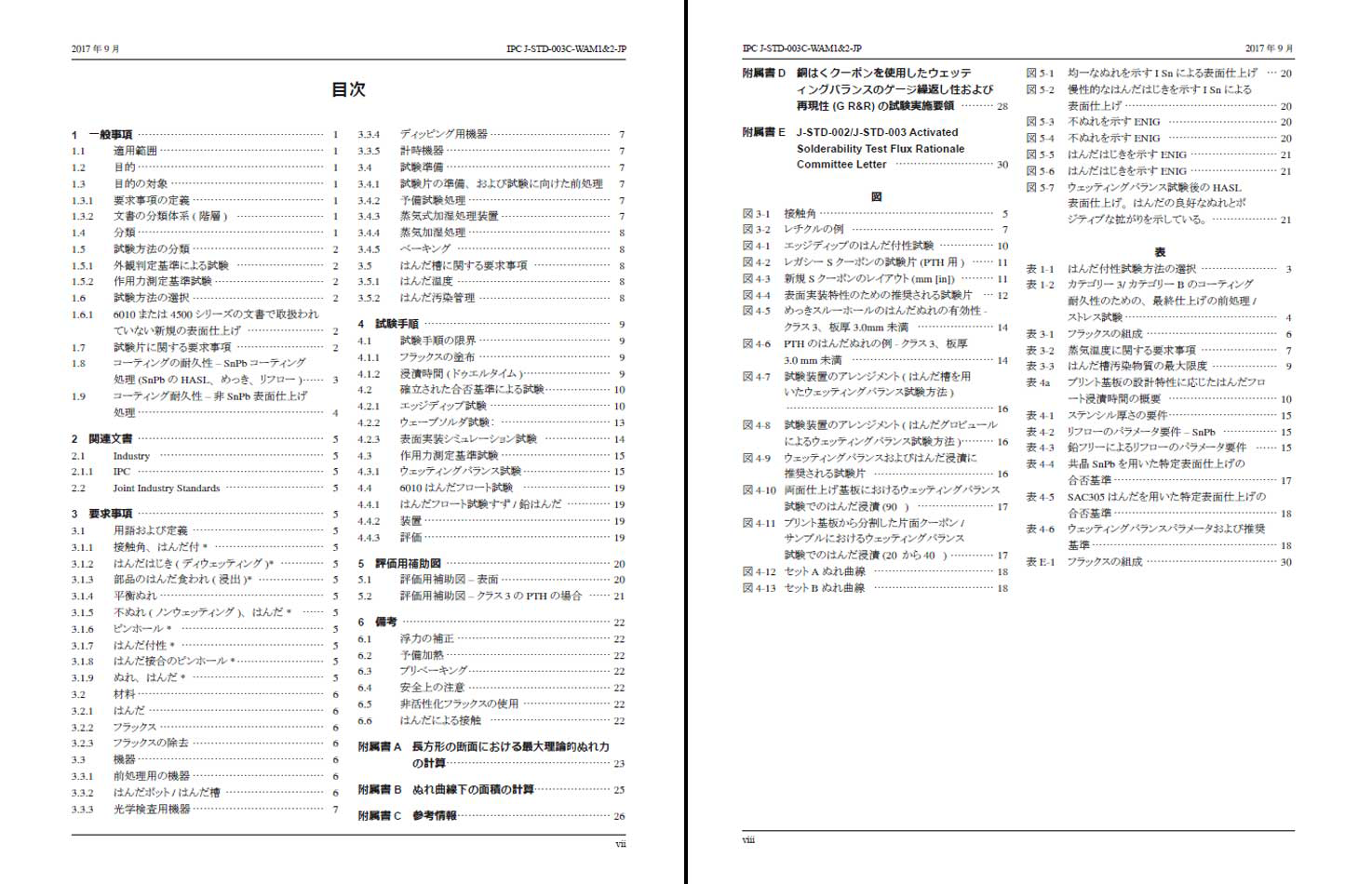

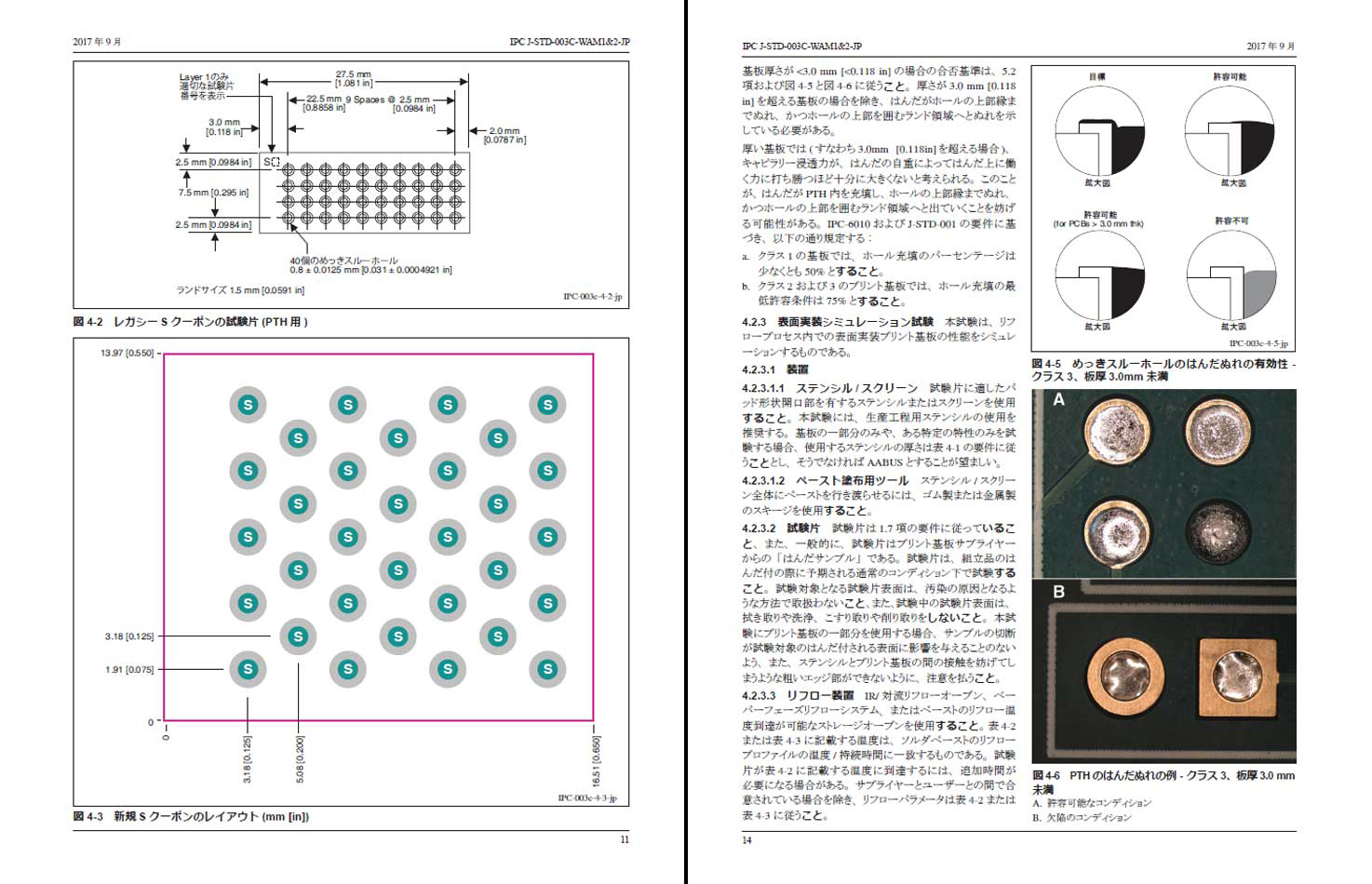

J-STD-003は、すず鉛または鉛フリーのはんだを使用しながら、プリント基板の表面導体、取付けランドおよびめっきスルーホールのはんだ付け性を評価するための試験方法や欠陥の定義について規定し、また図を示すものである。

本規格はベンダーおよびユーザーの両者による使用を目的としている。本規格はプリント基板の表面導体、取付けランドおよびめっきスルーホールがはんだと容易にぬれること、および過酷なプリント基板組立工程に耐えることに合格であると判定するためのはんだ付け性試験方法を提供することを目的としている。

本規格は表面導体(および取付けランド)とめっきスルーホールの両方のはんだ付け性を評価するための試験方法について説明している。リビジョン「C」には、はんだ付け性試験のGR&R (ゲージ繰返し性&再現性)に関する最新情報、およびアップデートされた図が掲載されている。

改訂版1は編集上の誤記を修正するとともに、ドキュメントの多くの領域に明確な記述を加えるものである。

本規格は、エレクトロニクス業界内で採用されるはんだ付け性試験の要求事項と試験方法を規定する2つの基準のうちの1つである。もう1つは、部品側のはんだ付け性について言及している。

最新日本語版バージョン:C

更新年:2017年(翻訳2020年)

全27ページ

David Adams, Rockwell Collins

Chris Alter, Honeywell

Bill Beair, Raytheon Company

James Bielick, IBM Corporation

Wendi Boger, TTM Technologies

Edwin Bradley, Motorola

Mark Buechner, BAE Systems

更新年:2017年(翻訳2020年)

全27ページ

David Adams, Rockwell Collins

Chris Alter, Honeywell

Bill Beair, Raytheon Company

James Bielick, IBM Corporation

Wendi Boger, TTM Technologies

Edwin Bradley, Motorola

Mark Buechner, BAE Systems

Thomas Carlstrom, Ericsson AB

Thomas Carroll, Boeing Company

Byron Case, L-3 Communications

Vanja Bukva, Teledyne Dalsa

Alejandro Cruz, Jabil Mexico

Don Dupriest, Lockheed Martin

Howard Feldmesser, Johns Hopkins

University

Rigo Garcia, NASA GSFC

Christian Klein, Robert Bosch

Jose Rios, Massachusetts Institute of

Technology

Thomas Carroll, Boeing Company

Byron Case, L-3 Communications

Vanja Bukva, Teledyne Dalsa

Alejandro Cruz, Jabil Mexico

Don Dupriest, Lockheed Martin

Howard Feldmesser, Johns Hopkins

University

Rigo Garcia, NASA GSFC

Christian Klein, Robert Bosch

Jose Rios, Massachusetts Institute of

Technology

English

English 中文

中文 Deutsch

Deutsch Español

Español